O advento dos chiplets • Artigos • Cascas de conhecimento, kits de design de chiplelet para integração heterogênea 3D IC | Software Siemens

Usando kits de design de chiplelet para ajudar a pavimentar o caminho para a integração heterogênea 3D IC

Alguns anos depois, os primeiros processadores apareceram com em particular o Intel 4004, relativamente simples hoje. Então os processadores se tornaram mais complexos.

O advento dos chiplets

Após uma discussão no JZDS e na discórdia, eu disse a mim mesma que escrever um artigo sobre os chiplets seria benéfico para o maior número. E manteria uma faixa escrita contrária ao que pode acontecer com os JZDs

Em vez de escrever um bilhete muito longo, eu preferia o formato do artigo para obter um pouco mais nos detalhes. Espero poder ensinar o que são os chiplets, por que essa tecnologia foi criada e por que ela se desenvolverá nos próximos anos.

- Preâmbulo

- Chiplet, Quésaco ?

- Aspectos econômicos dos chiplets

- Dois exemplos: AMD e Intel (Altera)

Preâmbulo

Este artigo fala sobre conceitos de computadores, eletrônicos e arquitetura de computadores que podem ser avançados o suficiente para certos leitores. Eu te ofereço um pouco de popularização neste preâmbulo para entender um pouco melhor do que estamos falando.

Para os puristas, os atalhos serão feitos, essa popularização poderá conter informações voluntariamente imprecisas para facilitar a compreensão.

Chiplet, Quésaco ?

Vamos começar com o mais difícil, definir o que é um chiplet !

De fato, o termo chiplet apareceu na década de 1970, mas seu uso foi retido principalmente nos últimos anos, para aqueles que estão interessados em processadores complexos ou chips eletrônicos como FPGA (chips cujas portas lógicas internas podem ser reprogramadas). Para os outros, na parte inferior da sala, você pode nunca ter ouvido falar desse termo, iremos remediar !

Vamos voltar à base do que é um chip eletrônico: um pedaço de silício gravado (os famosos transistores) que é encapsulado em um caso. Com os componentes de cruzamento, pequenos fios de ouro ou prata conectam as pernas do componente ao pedaço de silício. No início, os chips são compostos de transistores gravados com resoluções bastante grosseiras (em comparação com hoje) e as funções eram bastante básicas: portas lógicas, amplificadores operacionais etc. No entanto, já foi um enorme progresso em termos de miniaturização !

Naquela época, os componentes tinham pernas cruzando e é necessário conectar o chip de silício a essas pernas. É feito com finos filhos de prata ou ouro que são soldados entre o chip e as pernas dentro do estojo.

Alguns anos depois, os primeiros processadores apareceram com em particular o Intel 4004, relativamente simples hoje. Então os processadores se tornaram mais complexos.

A partir da década de 1970, a IBM desenvolveu componentes MCM (Multi-chodu) incluindo várias lascas de silício em um único caso. Mas essa tecnologia se desenvolverá principalmente no final dos anos 90. Podemos observar o Pentium Pro da Intel lançado em 1995. Esse processador incluiu dois chips de silício: um para o processador estritamente falando e outro para a memória de cache L2 (uma memória de buffer entre o processador e a RAM, muito mais rápida, mas muito mais cara porque gravada com o processador).

Como podemos ver na foto, os dois chips têm aproximadamente o mesmo tamanho e a Intel ofereceu vários tamanhos de cache L2. A vantagem de separar o processador de memória de cache era poder economizar escala no chip do processador, oferecendo tamanhos de memória de cache diferentes, colocando um chip de tamanho diferente no caso.

Esse tipo de componente permanece relativamente subdesenvolvido, mesmo que a IBM continuasse a desenvolver componentes do MCM. Observe o Power5 da IBM lançado em 2004, que vê quatro processadores diretamente com um chip de memória de cache L3. A interconexão de pulgas é feita dentro do caso.

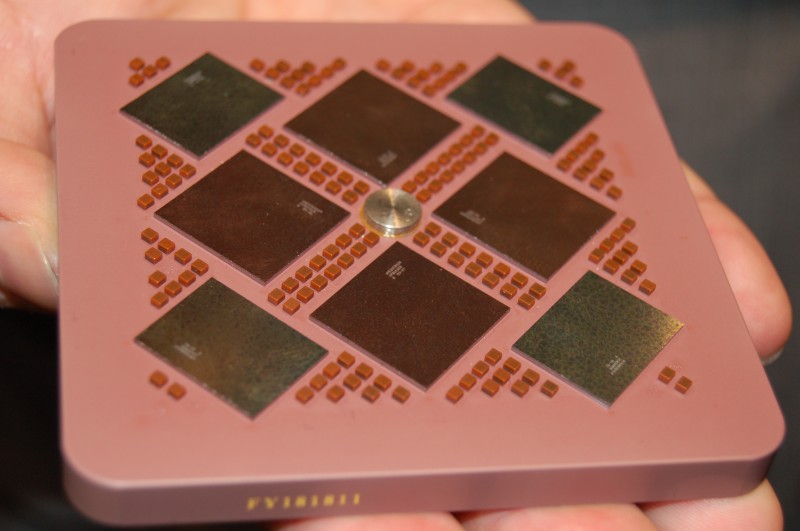

Hoje a tecnologia evoluiu e os chips MCM estão presentes em produtos de consumo com processadores AMD. Aqui podemos ver um processador EPYC 7702 (lançado em agosto de 2019) composto por 9 chips de silicone interconectados: 8 chips contendo núcleos e memória de cache e um chip central conectando o outro 8 e que gerencia o DDR, bem como os sinais d ‘entrada/ Saia (SATA, PCI Express, USB, etc.)).

Mas me diga Jamy, o que é um chiplet ?

Ah sim, eu derivei um pouco

De fato, um chiplet é um dos chips de silício presentes em um MCM. Um chiplet é feito para ser interconectado com outros chipets. Sim, é relativamente simples, mas você teve que mostrar algumas fotos boas para entender

No entanto, para ser um pouco mais preciso no significado dos chiplets, a idéia não é necessariamente colocar vários chips diferentes ligados. Há também uma noção de chip genérico que pode ser reutilizado e não dedicado a uma referência específica do processador.

Aspectos econômicos dos chiplets

Após esta introdução durante a imagem, vamos agora entender por que os chipets se desenvolverão no futuro. Para fazer isso, é necessário retornar ao processo de fabricação de pulgas eletrônicas.

Sente -se confortavelmente em uma poltrona porque a viagem da praia será longa

Não, espere !

Vamos gastar uma parte inteira da fabricação de silício. O que nos interessará é a distribuição de pulgas (morrer) no bolo de silício (wafer) e, em particular, a evolução do rendimento com o aumento da requinte de gravação.

Mas antes desse aspecto do rendimento, devemos falar sobre o tamanho físico máximo de um dado. De fato, em uma panqueca de silício, o mesmo design de um chip é repetido várias vezes (dezenas ou até centenas de vezes). A impressão deste design é feita opticamente via luz ultravioleta. No entanto, há todo um conjunto de lentes e mecanismos ópticos que impede a gravação de um único dado em todo o bolo de silício.

Quanto mais complicamos as pulgas, mais queremos colocar transistores, para que devemos aumentar o tamanho do chip ou aumentar a delicadeza da gravação para ajustar mais transistores na mesma superfície. Mas também existem outras restrições e limites.

É por isso que o princípio do chiplet é interessante para ignorar esses limites: use vários pequenos chips de silicum conectados para fazer um chip mais complexo, mas impossível de gravar.

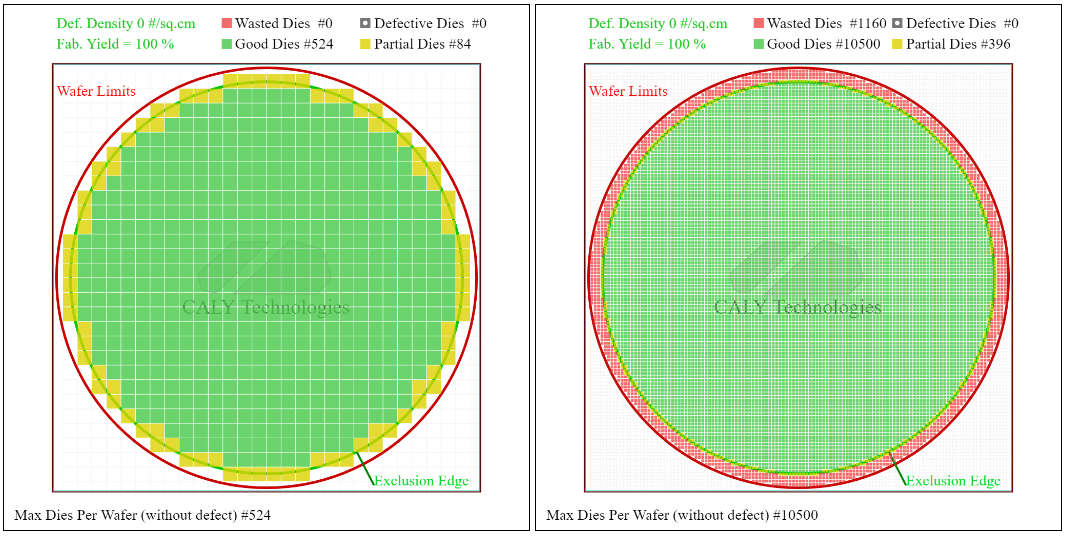

Agora de volta ao rendimento (colheita Em inglês). Primeiro, as bolachas estão de forma redonda e queremos gravá -las com batatas fritas retangulares. Todo o silício não é usado. Mas quanto menor as matrizes nas bordas e mais podemos ter matrizes inteiras. É o mesmo princípio que o alias em um videogame: quanto mais os pixels usados para formar uma forma redonda são pequenos e menos percebermos, mais nidando.

No exemplo acima, se relatarmos as matrizes parciais sobre o número total de matrizes (bom e viés), obtemos uma proporção de 13.8 % no caso de matrizes de 5 × 5 mm e 3.6 % no caso de 1 × 1 mm matrizes. Quanto menor a matriz, mais válidas matrizes podem ter nas bordas, o que aumenta o rendimento.

Você também pode fazer uma grande mistura de matriz no centro da bolacha e usar matrizes menores nas bordas para otimizar o rendimento devido ao alias.

Diga Jamy, por que usamos bolachas redondas para fazer pulgas retangulares ?

Bem, é por causa do método de fazer silício chamado processo Czochralski, que dá silício na forma de cilindros, cortados em fatias muito finas para dar bolachas.

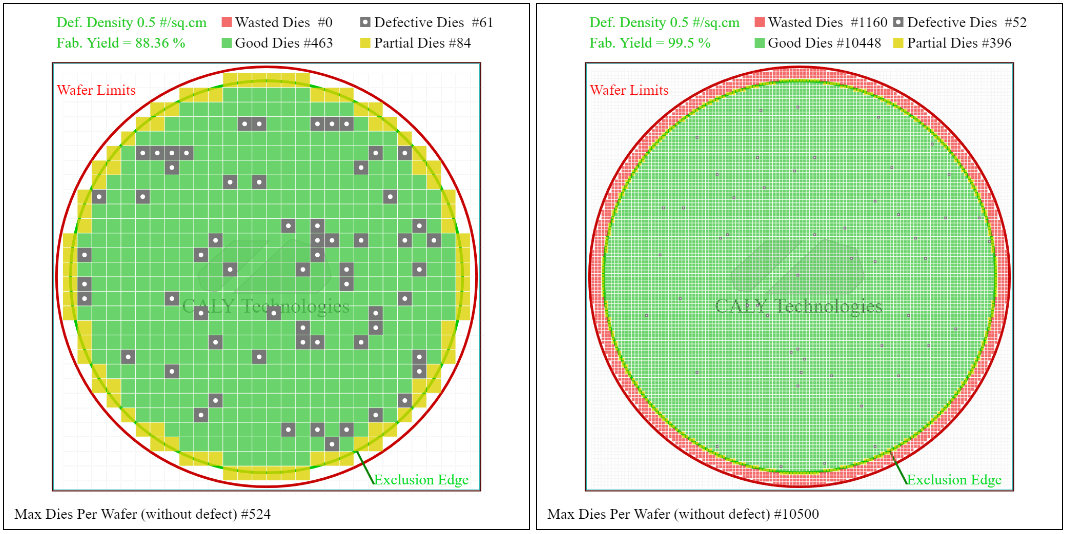

Segundo, o rendimento é afetado pelos defeitos que podem aparecer na bolacha. Você pode pensar em grãos de poeira que caem na bolacha.

Eu retomei o exemplo anterior adicionando uma densidade de falha de 0.5 por cm². Agora compare o Fabricação de rendimento que corresponde à proporção entre o número de matrizes funcionais e o número total de produtos produzidos. No caso de uma matriz de 5 × 5 mm, o rendimento é 88.4 %, enquanto com 1 × 1 mm matrizes, o rendimento é 99.5 %.

Portanto, é duplamente interessante ter pequenas matrizes para otimizar a produção de pulgas eletrônicas. No entanto, cortar um chip complexo em vários chips menores requer comunicação desses diferentes chips entre eles, devemos, portanto, adicionar elementos de comunicação que ocuparem espaço adicional e usar energia adicional.

Além disso, o uso de chiplets pode possibilitar o uso de matrizes de diferentes requintes da gravação de acordo com as funções que permitem modular os custos do chip final com o desempenho.

Finalmente, outro aspecto econômico a ver é a complexidade do desenvolvimento de novos recursos. Isso tende a ter empresas especializadas (ou pelo menos start-ups no início) oferecendo blocos de propriedade intelectual (funções) prontos para usar. Por exemplo, um fabricante de processadores poderá se concentrar no desenvolvimento do próprio processador ao comprar matrizes para funções como PCI Express, USB ou DDR Controllers.

Para facilitar a interoperabilidade de chiplets provenientes de diferentes fabricantes, grandes players como Intel, AMD, ARM, Qualcomm, Samsung ou TSMC criaram um padrão de comunicação entre Chiplets, UCIE (CHIPlet universal Interconect Express)).

Dois exemplos: AMD e Intel (Altera)

AMD Epyc

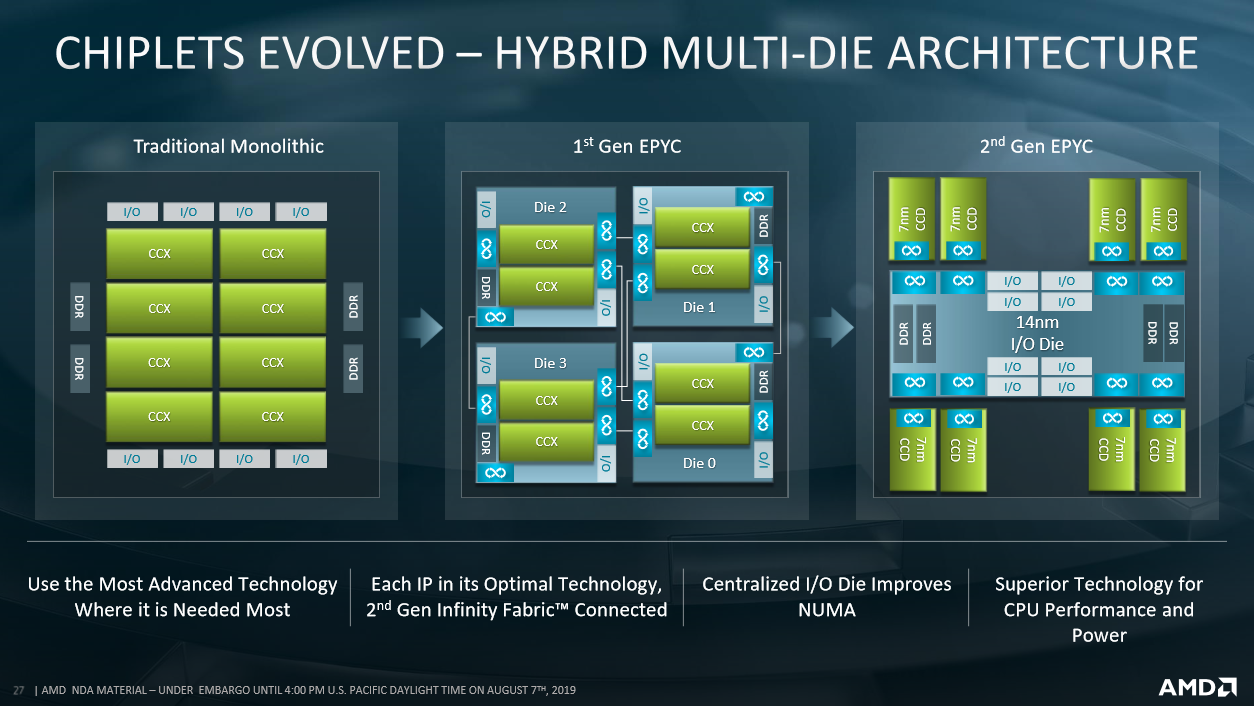

Hoje, mais e mais processadores usam esta técnica de chiplets. A AMD usa chiplets desde a primeira geração de processadores EPYC, onde os diferentes corações são ligados peloTecido infinito.

A primeira geração de processadores EPYC viu um conjunto de matrizes que poderiam ser equiparadas a processadores completos sendo vinculados peloTecido infinito Para formar o processador final. Os cliques eram, portanto, uma espécie de pequeno processador autônomo: cada matriz gerenciava suas entradas/saídas e tinha seu controlador DDR.

Esses matrizes, ou melhor, os chiplets têm dois Complexo de computação do núcleo (CCX, um conjunto de quatro núcleos com memória de cache), bem como um controlador DDR, gerencia entradas/saídas (PCI Express, por exemplo) e possui módulos de comunicação para oTecido infinito.

Pequena sutileza, sempre existem quatro chipets em um epyc de primeira geração. Para variar o número de corações, a AMD desativa os corações dentro do CCX. Por exemplo, para ter 24 núcleos, o CCX tem apenas 3 núcleos ativos

Esta primeira geração, portanto, usou o princípio dos chiplets como uma espécie de cópia/colada de matrizes, em vez de desenvolver uma grande matriz monolítica.

Para a segunda geração, a AMD empurra o conceito um pouco mais. De fato, os CCXs agora são independentes, agrupados em pares dentro de um Die de computação do núcleo (CCD) conectado por Tecido infinito para um dado que gerencia o DDR e as entradas/saídas chamadas E/S Die (IOD).

A AMD explora totalmente essa separação aumentada das funções. De fato, o CCD está gravado em 7 nm enquanto o IOD está gravado em 14 nm.

Abaixo de uma apresentação da AMD, resumindo a passagem em chiplets dos processadores EPYC.

Intel FPGA (Altera)

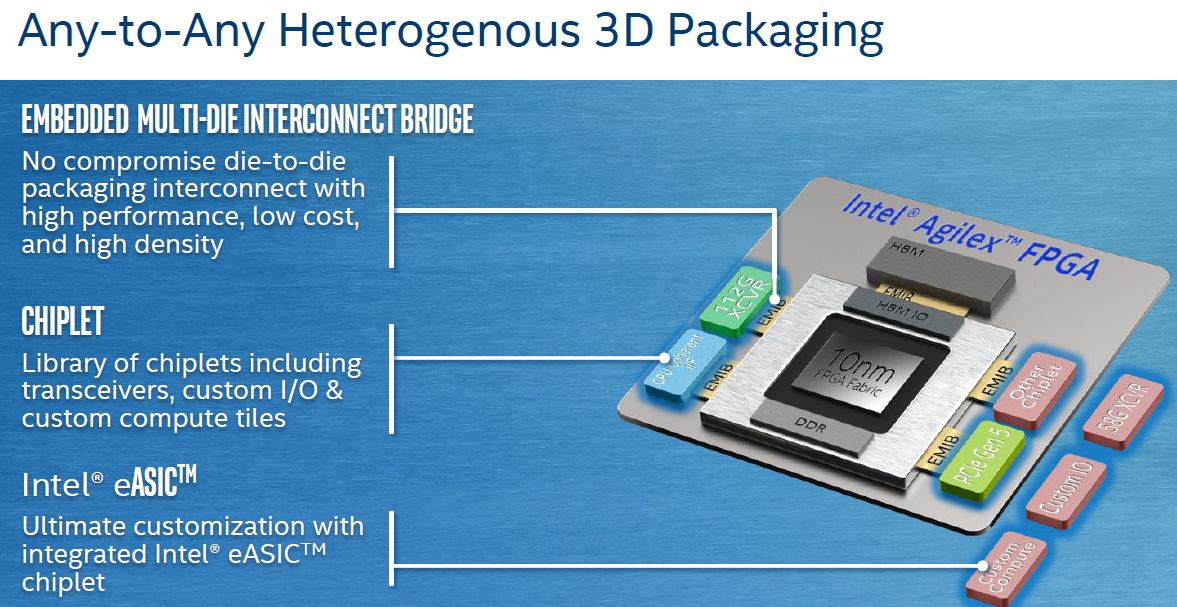

Os processadores Intel são sempre chips monolíticos, exceto algumas exceções, como poderíamos ver no início deste artigo. No entanto, no setor Intel FPGA (FPGA reconfigurável) usa chipets para a última geração, Agilex.

Esses chipets dizem respeito principalmente do tipo de transcensa usada (links rápidos) e são chamados Azulejos. Se a Intel oferece variações predefinidas a partir desses ladrilhos, deve ser possível ter chips personalizados para suas próprias necessidades.

Os ladrilhos são divididos pela velocidade máxima dos transceptores e pelos protocolos suportados (Ethernet, PCI Express, etc.): 16g para p, 28g para h, 32g para r, etc.

A Intel também evoca para o futuro a possibilidade de conectar chiplets personalizados que forneçam funções adicionais. Atualmente, as empresas lançaram um chiplet ADC/DAC (Jariett Technologies), bem como outra conexão óptica (Ayar Labs).

Finalmente não devemos acreditar também que os chips monolítico está morto. Eles sempre têm vantagens, especialmente em termos de comunicação interna e latência, o que pode ser crítico para certas aplicações que requerem chips de tamanho grande.

Este é o caso da Broadcom e seu switch 400G Chips cuja escolha é explicada pelo designer neste vídeo: https: // www.YouTube.Com/relógio?V = b-coGMBAUG4

Espero que este artigo tenha mais para você e tenha permitido que você soubesse um pouco mais sobre a fabricação de chips atuais. Tentei popularizar um assunto complexo, também espero poder mantê -lo depois do primeiro parágrafo

Não hesite em deixar um comentário se certos pontos permanecerem enigmáticos para você, tentarei fornecer detalhes.

6 comentários

Esta resposta foi útil

Excelente artigo, obrigado @ zeql !

“Jogue -me para os lobos e eu voltarei o pacote.” – Seneca

Esta resposta foi útil

Eu queria saber o quanto o advento dos chiplets foi capaz de considerar uma certa evolução em hardware (também grau de consumidor que grau de servidor) no futuro, ou mesmo uma mudança de paradigma na maneira como projetamos máquinas altamente e ótimas em geral.

Certos sistemas bem integrados (especialmente na Apple) não se baseiam apenas em uma CPU “clássica” muito eficiente, mas também em vários chips auxiliares especializados que descarregam CPUs generalistas. Em um sistema limitado como um smartphone, podemos encontrar chips de transcodificação H265, unidades de cálculo para ai (Motor neural da Apple) e, claro, a unidade gráfica clássica.

Portanto, adoto o diagrama da AMD Epyc da 2ª geração e me pergunto se os chiplets seriam uma maneira simples de produzir comercialmente e industrialmente viável a partir das unidades completas que embarcam vários chips especializados para obter desempenho ideal em determinadas tarefas. Por exemplo, uma unidade poderia fornecer CCDs clássicos, mas também um DSP, uma GPU, Transco H265/AV1/VP9/…, um chip para fazer AES, etc. e conecte tudo através do IOD/Infinity Manufacture. Cada fabricante de máquinas/servidores pode, portanto, compor sua unidade final pronta para uso, tendo se compunhado e sem P&D/custos de industrialização faramineurosos.

Isso me lembra o conceito de Apu, mas não sei se há um relatório.

Esta resposta foi útil

Eu queria saber o quanto o advento dos chiplets foi capaz de considerar uma certa evolução em hardware (também grau de consumidor que grau de servidor) no futuro, ou mesmo uma mudança de paradigma na maneira como projetamos máquinas altamente e ótimas em geral.

Certos sistemas bem integrados (especialmente na Apple) não se baseiam apenas em uma CPU “clássica” muito eficiente, mas também em vários chips auxiliares especializados que descarregam CPUs generalistas. Em um sistema limitado como um smartphone, podemos encontrar chips de transcodificação H265, unidades de cálculo para ai (Motor neural da Apple) e, claro, a unidade gráfica clássica.

Portanto, adoto o diagrama da AMD Epyc da 2ª geração e me pergunto se os chiplets seriam uma maneira simples de produzir comercialmente e industrialmente viável a partir das unidades completas que embarcam vários chips especializados para obter desempenho ideal em determinadas tarefas. Por exemplo, uma unidade poderia fornecer CCDs clássicos, mas também um DSP, uma GPU, Transco H265/AV1/VP9/…, um chip para fazer AES, etc. e conecte tudo através do IOD/Infinity Manufacture. Cada fabricante de máquinas/servidores pode, portanto, compor sua unidade final pronta para uso, tendo se compunhado e sem P&D/custos de industrialização faramineurosos.

Isso me lembra o conceito de Apu, mas não sei se há um relatório.

Portanto, você deve saber que um chip é frequentemente feito com IP (propriedade intelectual): uma função vendida bastante pronta no nível “transistores”, mas que deve ser integrada ao seu design.

Um exemplo clássico é um controlador DDR3 no microcontrolador de placas. O fabricante do microcontrolador não domina necessariamente o DDR3 e não possui as habilidades, o tempo (nem o desejo) de criar um controlador DDR3. Ele, portanto, compra um IP de um controlador e o integra em seu design.

Você tem que ter sucesso em ver a diferença entre a possibilidade de um IP e um chiplet. Para mim, o chiplet existe e trazer um ou mais recursos avançados e que já passaram nos testes da gravação, portanto, uma etapa adicional no design. Mas ainda existe o problema de testar o solo completo com todos os chiplets. Portanto, não podemos criar centenas de variações como um lego. É preciso um mínimo de realidade econômica.

Mas sim, para um certo volume, podemos criar soquetes à la carte.

A grande vantagem está no lado da produção do chip: se um IP puder ser recusado para uma delicadeza de gravação diferente, um chiplet para a vantagem de poder sempre ser gravado em sua delicadeza inicial (se for suficiente) quando outras peças podem ser melhorado com uma gravação menor.

Esta resposta foi útil

Além disso, eu pensei que os chiplets poderiam ser usados em um design modular. Você pega um design com 4 fichas, as pulgas com falhas são distribuídas ao longo da produção, e aqueles com 3 chips que funcionam em 4 serão um intervalo abaixo e um pouco mais barato do que aqueles com os 4 que funcionam.

Que simplifica o design e a industrialização em relação à operação convencional.

Amante de software livre e distribuição GNU/Linux Fedora. #Jesuisarius

Esta resposta foi útil

Obrigado por este mega artigo interessante. Eu te adoraria muito tempo para detalhar cada ponto que você não explica no tutorial para realmente entender as coisas, mas interessante de qualquer maneira .

Usando kits de design de chiplelet para ajudar a pavimentar o caminho para a integração heterogênea 3D IC

Um chiplet é uma matriz ASIC, projetada e otimizada para operação dentro de um pacote em conjunto com outros chiplets. Integrada heterogênea (HI) envolve matriz ou chipets inteiros e chipets em chipplets de sistema em pacote (SIP). Esses dispositivos se ofereceram benefícios consideráveis, incluídos no desempenho, poder, área, custo e TTM.

A troca de design de chiplelet (CDX) consiste em fornecedores de EDA, chiplet

Provedores/montadores e integradores SIP e é um grupo de trabalho aberto para recomendar modelos de chiplet e fluxos de trabalho padronizados para facilitar um ecossistema de chiplelet. Este webinar resume os kits de design de chiplet (CDKS) para ajudar a padronizar 2.5d e 3.D Designs IC para criar um ecossistema aberto.

Construindo um ecossistema para 2 bem -sucedido.Integração do modelo de chiplet 5D e 3D

Semelhante a um processo SoC, você precisa de um ecossistema para chiplets. A chave permite a adoção geral do mercado e a implantação de projetos baseados em chiplelets incluídos:

- Tecnologia: 2.5 D Interposição e processos de fabricação e montagem empilhados em 3D

- IP: modelos de chiplet padronizados

- Fluxos de trabalho: Fluxos de design da EDA e PDK, CDK, DRM e Regras de Assembléia

- Modelos de negócios: Chiplet Marketplace

O foco inicial do CDX é 2.Modelos de chiplet baseados em interposição de 5D com 3D para seguir. Saiba mais sobre esses esforços no webinar.

A troca de design de chiplelet (CDX) consiste em fornecedores de EDA, provedores de chipletos/montadores e integradores SIP e é um grupo de trabalho aberto para recomendar modelos e fluxos de trabalho padronizados para facilitar um ecossistema de chiplet. Este webinar resume os kits de design de chiplet (CDKS) para ajudar a padronizar 2.5d e 3.D Designs IC para criar um ecossistema aberto.

Construindo um ecossistema para 2 bem -sucedido.Integração do modelo de chiplet 5D e 3D

Semelhante a um processo SoC, você precisa de um ecossistema para chiplets. A chave permite a adoção geral do mercado e a implantação de projetos baseados em chiplelets incluídos:

- Tecnologia: 2.5 D Interposição e processos de fabricação e montagem empilhados em 3D

- IP: modelos de chiplet padronizados

- Fluxos de trabalho: Fluxos de design da EDA e PDK, CDK, DRM e Regras de Assembléia

- Modelos de negócios: Chiplet Marketplace

O foco inicial do CDX é 2.Modelos de chiplet baseados em interposição de 5D com 3D para seguir. Saiba mais sobre esses esforços no webinar.

A imagem vazada revela um design ambicioso de chiplet para a GPU AMD Radeon

A imagem vazada revela um design ambicioso de chiplet para a GPU AMD Radeon

- por

- Em notícias

- em 16 de agosto de 2023

Uma imagem vazada surgiu, revelando um design de GPU com chiplets Radeon, supostamente de um projeto cancelado do Chip 4C 4C 4C. O design presente entre 13 e 20 Chiplets diferentes em uma única GPU, testemunhando a abordagem ambiciosa da AMD. Este design de chiplet mais complexo difere do Navi 31 Silicon usado atualmente no Radeon RX 7900 XTX. Embora a iteração anterior da GPU tenha sido considerada uma primeira geração, ela não usava um design de chiplet real como os recentes processadores Ryzen da AMD. No entanto, a concepção do NAVI 4C divulgada representa um avanço significativo, porque incorpora vários chiplets de cálculo, bem como chiplets de E/S distintos, em um único substrato. A imagem vazada apresenta 13 chipets, com a possibilidade de chips adicionais do controlador de memória não exibidos na imagem.

Para confirmar a autenticidade da imagem, uma patente relevante de 2021 discutindo o conceito de modularidade em processadores paralelos é destacada. Os padrões de patente se assemelham ao design mostrado na imagem vazada, até sugerindo a possibilidade de mais chiplets do outro lado do copo transversal.

Infelizmente, o design da GPU apresentado na imagem vazada foi cancelado. Isso concorda com relacionamentos recentes, sugerindo que o sotaque da AMD para a próxima geração de GPU estará no NAVI 43 e NAVI 44 Chips monolíticos destinados ao público em geral, e não em componentes altos. No entanto, especula -se que a AMD redirecre seus esforços para o desenvolvimento de uma GPU composta por vários chiplets de cálculo para o segmento alto de sua gama futura de placas gráficas, potencialmente com rDNA 5.

Embora a realização de vários chipets de cálculo para gráficos de jogos seja mais complexa do que para os cálculos tradicionais da CPU, a decisão da AMD de superar os obstáculos do projeto agora e trabalhar em uma solução melhor para o rDNA 5 é percebida como uma etapa positiva. Teria sido vantajoso para a AMD ter um plano de resgate, como um novo nó para uma versão aprimorada do Navi 31.