Apariția cipurilor • Articole • Zest of Cunoaștere, kituri de proiectare a cipului pentru integrare eterogenă 3D IC | Software -ul Siemens

Utilizarea kiturilor de design de cipuri pentru a ajuta la deschiderea drumului pentru integrarea eterogenă 3D IC

Câțiva ani mai târziu, primele procesoare au apărut în special Intel 4004, relativ simplu astăzi. Atunci procesoarele au devenit mai complexe.

Apariția cipurilor

În urma unei discuții în JZDS și pe discordie, mi -am spus că scrierea unui articol despre Chiplets ar fi benefic pentru cel mai mare număr. Și ar păstra o piesă scrisă contrar a ceea ce se poate întâmpla cu JZD -urile

În loc să scriu un bilet foarte lung, am preferat formatul articolului pentru a obține ceva mai mult în detalii. Sper să vă pot învăța care sunt chipletele, de ce a fost creată această tehnologie și de ce se va dezvolta în anii următori.

- Preambul

- Chiplet, Quésaco ?

- Aspecte economice ale cipurilor

- Două exemple: AMD și Intel (ALTERA)

Preambul

Acest articol vorbește despre concepte de calculator, electronice și arhitectură ale computerelor, care pot fi suficient de avansate pentru anumiți cititori. Vă ofer o mică popularizare în acest preambul pentru a înțelege puțin mai bine despre ce vorbim.

Pentru puriști, vor fi făcute comenzi rapide, această popularizare poate fi capabilă să conțină informații imprecise voluntar pentru a facilita înțelegerea.

Chiplet, Quésaco ?

Să începem cu cei mai dificili, să definim ce este un chiplet !

Într -adevăr, termenul de cip a apărut în anii ’70, dar utilizarea sa a decolat în principal în ultimii ani, pentru cei care sunt interesați de procesoare complexe sau jetoane electronice, cum ar fi FPGA (cipuri ale căror uși logice interne pot fi reprogramate). Pentru ceilalți, în partea de jos a camerei, poate nu ați auzit niciodată de acest termen, îl vom remedia !

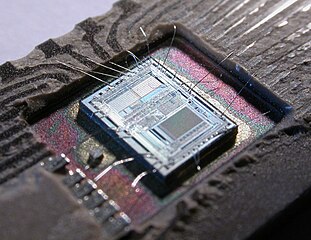

Să ne întoarcem la baza a ceea ce este un cip electronic: o bucată de siliciu gravat (celebrele tranzistoare) care este încapsulată într -un caz. Cu componentele de traversare, firele minuscule de aur sau argint conectează picioarele componentei la bucata de siliciu. La început, jetoanele sunt alcătuite din tranzistoare gravate cu rezoluții destul de grosiere (în comparație cu astăzi), iar funcțiile au fost destul de de bază: uși logice, amplificatoare operaționale etc. Cu toate acestea, a fost deja un progres enorm în ceea ce privește miniaturizarea !

În acel moment, componentele aveau picioare de traversare și este necesar să conectăm cipul de siliciu la aceste picioare. Este fabricat cu fii subțiri de argint sau aur care sunt sudate între cip și picioarele din interiorul carcasei.

Câțiva ani mai târziu, primele procesoare au apărut în special Intel 4004, relativ simplu astăzi. Atunci procesoarele au devenit mai complexe.

Din anii ’70, IBM a dezvoltat componente MCM (Multi-codu) inclusiv mai multe jetoane de siliciu într -un singur caz. Dar această tehnologie se va dezvolta în principal la sfârșitul anilor 90. Putem nota pe Pentium Pro de Intel lansat în 1995. Acest procesor a inclus două jetoane de siliciu: unul pentru procesor strict vorbind și altul pentru memoria cache L2 (o memorie tampon între procesor și RAM, mult mai rapid, dar mult mai scump, deoarece este gravat cu procesorul).

După cum putem vedea în fotografie, cele două jetoane au aproximativ aceeași dimensiune și Intel a oferit mai multe dimensiuni de cache L2. Avantajul separării procesorului de memorie cache a fost să poată salva scala pe cipul procesorului, oferind în același timp dimensiuni diferite de memorie cache, punând un cip de dimensiuni diferite în caz.

Acest tip de componentă rămâne relativ subdezvoltat, chiar dacă IBM a continuat să dezvolte componente MCM. Rețineți Power5 de IBM lansat în 2004, care vede patru procesoare în mod clar cu un cip de memorie Cache L3. Interconectarea puricilor se face în interiorul cazului.

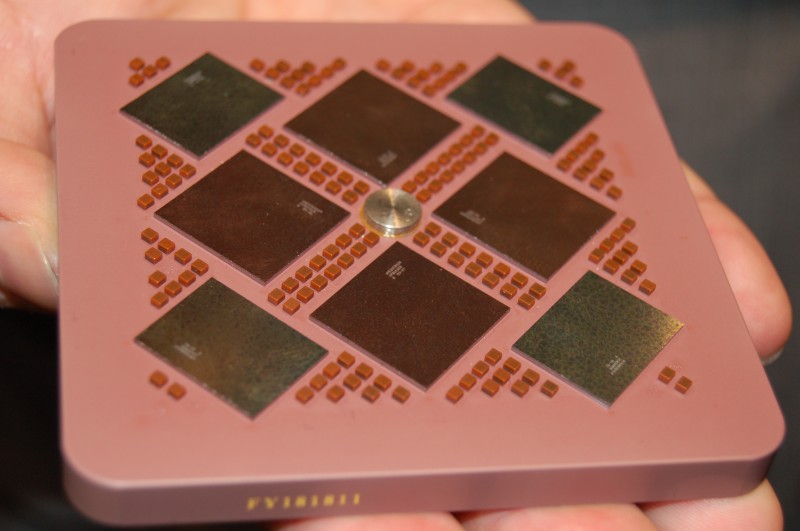

Astăzi tehnologia a evoluat, iar jetoanele MCM sunt prezente în produsele de consum cu procesoare AMD. Aici putem vedea un procesor EPYC 7702 (lansat în august 2019) compus din 9 jetoane de siliciu interconectate: 8 jetoane care conțin nuclee și memorie cache și un cip central care leagă celelalte 8 și care gestionează DDR -ul, precum și semnalele d ‘intrare/ Ieșire (SATA, PCI Express, USB, etc.)).

Dar spune -mi Jamy, ce este un chiplet ?

Ah, da, am derivat puțin

De fapt, un chiplet este unul dintre jetoanele de siliciu prezente într -un MCM. Un chiplet este făcut pentru a fi interconectat cu alte cipuri. Da, este relativ simplu, dar a trebuit să arăți câteva fotografii frumoase de înțeles

Cu toate acestea, pentru a fi puțin mai precis pe sensul cipurilor, ideea nu este neapărat să punem mai multe jetoane diferite legate între ele. Există, de asemenea, o noțiune de cip generic care poate fi reutilizată și care nu este dedicată unei anumite referințe de procesor.

Aspecte economice ale cipurilor

După această introducere în timp ce imaginea, să înțelegem acum de ce se vor dezvolta chipletele în viitor. Pentru a face acest lucru, este necesar să reveniți la procesul de fabricare a puricilor electronice.

Stai confortabil într -un fotoliu, deoarece călătoria de pe plaja cu nisip va fi lungă

Nu așteptați !

Vom petrece o parte întreagă din fabricarea siliciului. Ceea ce ne va interesa este distribuirea puricilor (a muri) pe tortul de siliciu (placă) și, în special, evoluția randamentului odată cu creșterea gravurii finețe.

Dar înainte de acest aspect al randamentului, trebuie să vorbim despre dimensiunea maximă fizică a unei matrițe. Într -adevăr, pe o clătită de siliciu, același design al unui cip se repetă de mai multe ori (zeci sau chiar de sute de ori). Impresia acestui design se face optic prin intermediul luminii ultraviolete. Cu toate acestea, există un set întreg de lentile și mecanisme optice care împiedică gravarea unei singure morți pe întregul tort de siliciu.

Cu cât complicăm mai mult puricii, cu atât dorim să punem tranzistoare, așa că trebuie să creștem dimensiunea cipului, fie să creștem delicatețea gravurii pentru a se potrivi mai multor tranzistoare pe aceeași suprafață. Dar sunt resimțite și alte constrângeri și limite.

Acesta este motivul pentru care principiul chipletului este interesant pentru a ocoli aceste limite: folosiți mai multe cipuri mici de silicum conectate împreună pentru a face un cip mai complex, dar imposibil de gravat într -un mod monolitic.

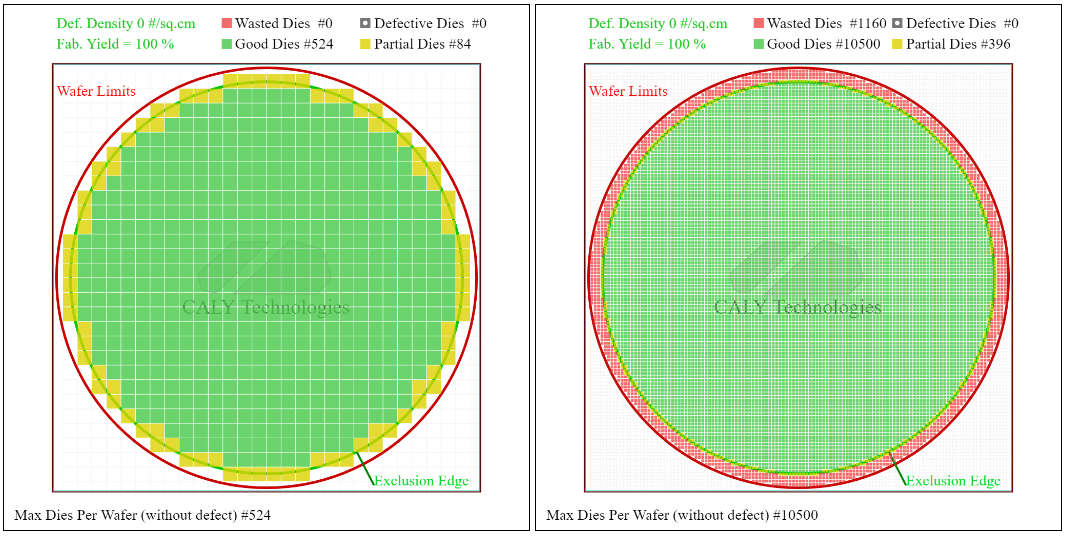

Acum înapoi la randament (Randament în limba engleză). În primul rând, napolitarii au o formă rotundă și vrem să o gravăm cu chipsuri dreptunghiulare. Întregul siliciu nu este folosit. Dar cu cât morții sunt mai mici la margini și cu atât mai mult putem avea matrițe întregi. Este același principiu ca aliasing -ul într -un joc video: cu atât pixelii obișnuiau să formeze o formă rotundă sunt mici și cu atât mai puțin ne dăm seama.

În exemplul de mai sus, dacă raportăm parțial matrițe pentru numărul total de matrițe (bune și părtinire), obținem un raport de 13.8 % în cazul matrițelor de 5 × 5 mm și 3.6 % în cazul 1 × 1 mm moare. Cu cât este mai mică, cu atât mai multe mori mai valide pot avea pe margini, ceea ce crește randamentul.

Puteți face, de asemenea, un amestec mare de matriță în centrul plafonului și puteți folosi matrițe mai mici la margini pentru a optimiza randamentul din cauza aliasului.

Spune Jamy, de ce folosim napolitane rotunde pentru a face purici dreptunghiulare ?

Ei bine, se datorează metodei de a face siliciu numit proces Czochralski, care dă siliciu sub formă de cilindri, tăiați în felii foarte fine pentru a da placi.

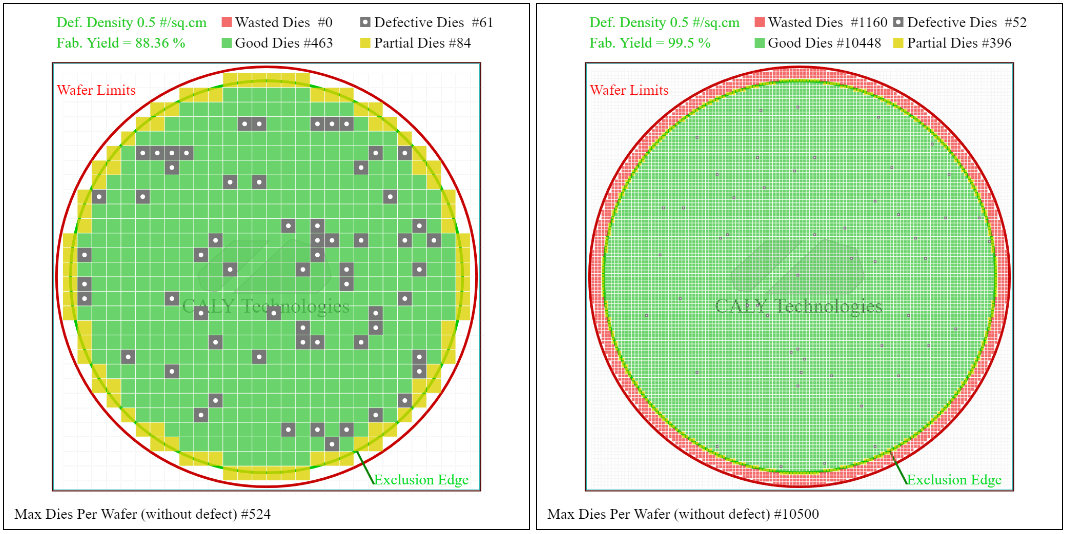

În al doilea rând, randamentul este afectat de defectele care pot apărea pe placă. Vă puteți gândi la cereale de praf care cad pe placă.

Am reluat exemplul anterior adăugând o densitate de eroare de 0.5 pe cm². Acum comparați Producția de producție ceea ce corespunde raportului dintre numărul de matrițe funcționale și numărul total de produse produse. În cazul unei matrițe de 5 × 5 mm, randamentul este de 88.4 % în timp ce cu 1 × 1 mm moare, randamentul este de 99.5 %.

Prin urmare, este de două ori interesant să aveți matrițe mici pentru a optimiza producția de purici electronici. Cu toate acestea, reducerea unui cip complex în mai multe jetoane mai mici necesită comunicarea acestor jetoane diferite între ele, trebuie să adăugăm elemente de comunicare care vin să ocupe un spațiu suplimentar și să utilizăm energie suplimentară.

În plus, utilizarea cipurilor poate face posibilă utilizarea matriilor de diferite finețe de gravură în funcție de funcțiile care permit modularea costurilor cipului final cu performanța.

În cele din urmă, un alt aspect economic de văzut este complexitatea dezvoltării de noi caracteristici. Acest lucru tinde să aibă companii specializate (sau cel puțin start-up-uri la început) care oferă blocuri de proprietăți intelectuale (funcții) gata de utilizare. De exemplu, un producător de procesoare se va putea concentra pe dezvoltarea procesorului în sine, în timp ce cumpărarea moare pentru funcții precum PCI Express, USB sau Controlere DDR.

Pentru a facilita interoperabilitatea cipurilor care provin de la diferiți producători, jucători importanți precum Intel, AMD, ARM, Qualcomm, Samsung sau TSMC au creat un standard de comunicare între Chipplets, UCIE (Universal Chiplet Interconect Express)).

Două exemple: AMD și Intel (ALTERA)

AMD EPYC

Astăzi din ce în ce mai mulți procesoare folosesc această tehnică Chiplets. AMD folosește cipuri de la prima generație de procesoare EPYC, unde diferitele inimi sunt legate între ele deȚesătură infinită.

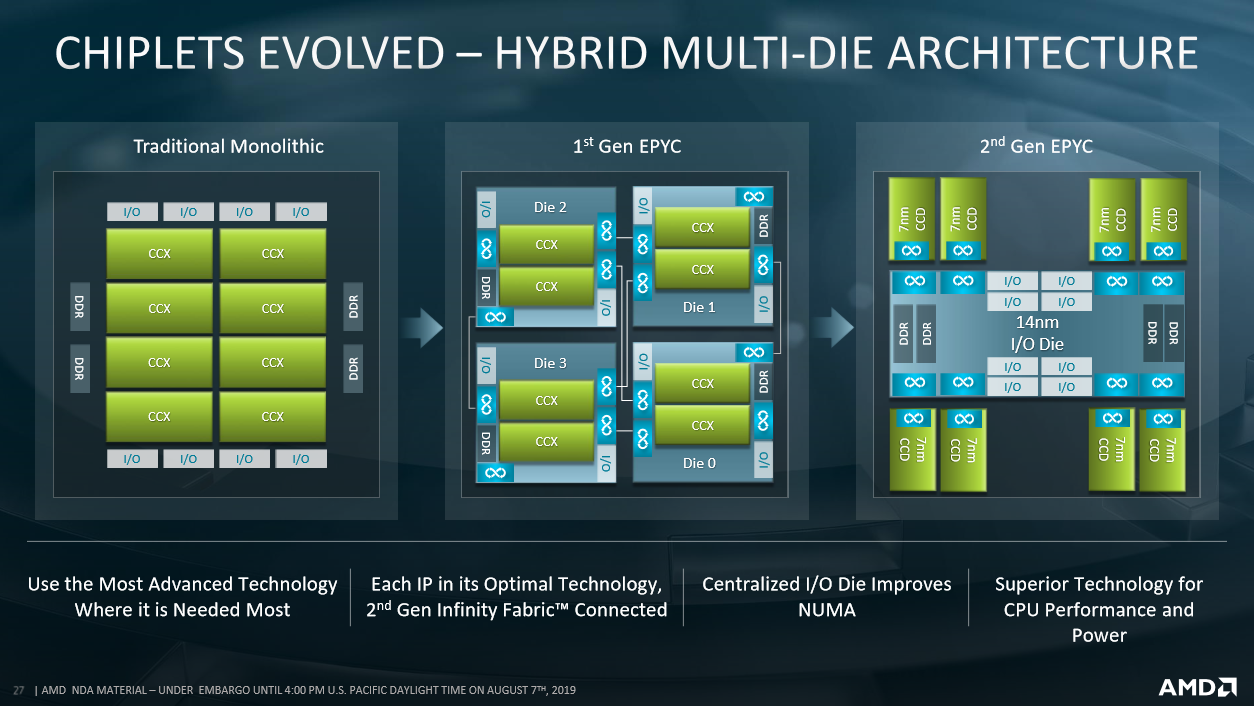

Prima generație de procesoare EPYC a văzut un set de matrițe care ar putea fi echivalate cu procesoarele complete legate între ele deȚesătură infinită Pentru a forma procesorul final. Prin urmare, chipletele erau un fel de mic procesor autonom: fiecare matriță și -a gestionat intrările/ieșirile și avea controlerul DDR.

Aceste matrițe, sau mai degrabă cipuri, au două Complex de calcul de bază (CCX, un set de patru nuclee cu memorie cache), precum și un controler DDR, gestionează intrări/ieșiri (PCI Express, de exemplu) și are module de comunicare pentruȚesătură infinită.

Subtilitate mică, există întotdeauna patru cipuri pe un EPYC din prima generație. Pentru a varia numărul de inimi, AMD dezactivează inimile în interiorul CCX. De exemplu, pentru a avea 24 de nuclee, CCX are doar 3 nuclee active

Prin urmare, această primă generație a folosit principiul chipletilor ca un fel de copie/lipit de matrițe în loc să dezvolte o mare matriță monolitică.

Pentru a doua generație, AMD împinge conceptul puțin mai departe. Într -adevăr, CCX -urile sunt acum independente, grupate în perechi în cadrul unui Core Calculare matriță (CCD) conectat de Țesătură infinită la o matriță gestionând DDR și intrările/ieșirile numite I/O Die (IOD).

AMD exploatează pe deplin această separare sporită de funcții. Într -adevăr, CCD este gravat în 7 nm, în timp ce IOD este gravat în 14 nm.

Mai jos o prezentare AMD care rezumă pasajul în cipuri ale procesoarelor EPYC.

Intel FPGA (ALTERA)

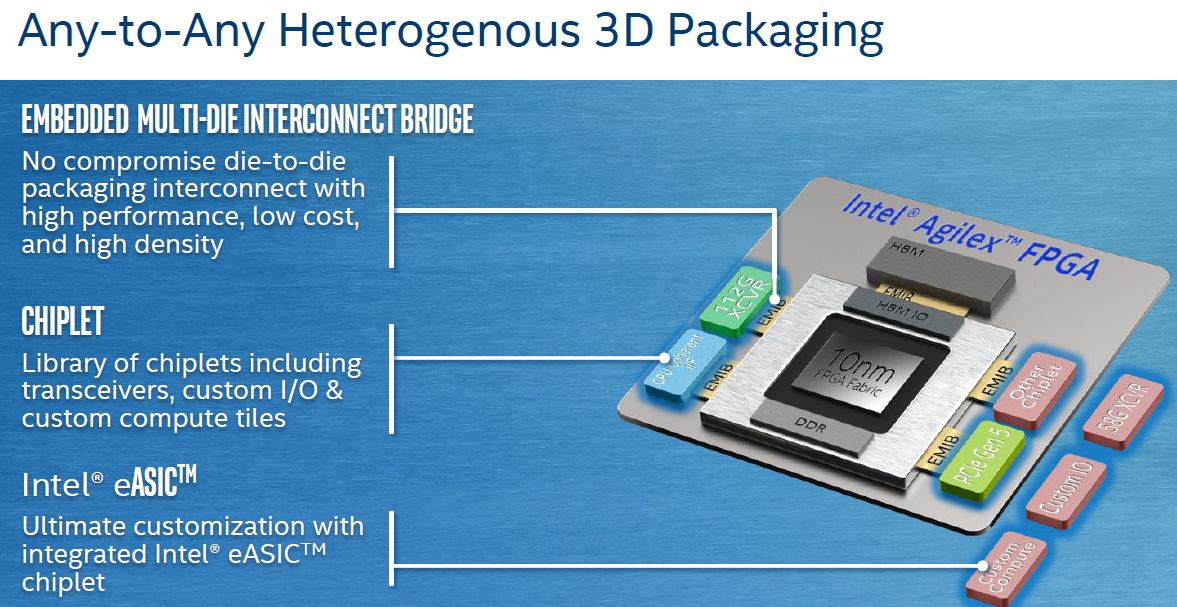

Procesoarele Intel sunt întotdeauna jetoane monolitice, cu excepția câtorva excepții așa cum am putea vedea la începutul acestui articol. Cu toate acestea, în sectorul Intel FPGA (reconfigurabil FPGA) folosește chiplete pentru ultima generație, Agilex.

Aceste cipuri se referă în principal la tipul de transcense utilizat (legături rapide) și sunt numite Plăci. Dacă Intel oferă intervale predefinite de la aceste plăci, trebuie să fie posibil să aveți jetoane personalizate pentru propriile nevoi.

Placile sunt împărțite la viteza maximă a transceiverilor și a protocoalelor acceptate (Ethernet, PCI Express etc.): 16g pentru P, 28g pentru H, 32G pentru R, etc.

Intel evocă, de asemenea, pentru viitor posibilitatea de a conecta cipuri personalizate care ar oferi funcții suplimentare. În prezent, companiile au lansat un cip ADC/DAC (Jariett Technologies), precum și o altă conexiune optică (Ayar Labs).

În cele din urmă, nu trebuie să credem nici că jetoanele monolitic sunt morți. Au întotdeauna avantaje, în special în ceea ce privește comunicarea internă și latența, ceea ce poate fi esențial pentru anumite aplicații care necesită cipuri cu dimensiuni mari.

Acesta este cazul Broadcom și al switch -ului său 400g jetoane a căror alegere este explicată de designer în acest videoclip: https: // www.YouTube.Com/ceas?V = b-cogmbaug4

Sper că acest articol are mai mult pentru tine și îți va permite să știi ceva mai multe despre fabricarea de jetoane curente. Am încercat să popularizez un subiect complex, sper și că am putut să te păstrez după primul paragraf

Nu ezitați să lăsați un comentariu dacă anumite puncte rămân criptice pentru dvs., voi încerca să ofer detalii.

6 comentarii

Acest răspuns a fost util

Articol excelent, mulțumesc @ zeql !

„Aruncă -mă la lupi și voi returna pachetul.” – Seneca

Acest răspuns a fost util

Mă întrebam cât de mult a reușit să ia în considerare o anumită evoluție în hardware (de asemenea Consumator-grad acea server-grade) în viitor, sau chiar o schimbare de paradigmă pe modul în care proiectăm mașini extrem de optime în general.

Anumite sisteme bine integrate (în special la Apple) nu se bazează exclusiv pe un procesor „clasic” foarte eficient, ci și pe mai multe jetoane auxiliare specializate care descarcă procesoare generaliste. Într -un sistem limitat ca smartphone, putem găsi jetoane de transcodare H265, unități de calcul pentru AI (Motor neural Apple) și, desigur, unitatea grafică clasică.

Prin urmare, preiau diagrama AMD EPYC de a 2 -a generație și mă întreb dacă Chiplets ar fi o modalitate simplă de a produce viabil din punct de vedere comercial și industrial din unitățile complete care îmbarcă mai multe cipuri specializate pentru a obține performanțe optime în anumite sarcini. De exemplu, o unitate ar putea asigura CCD -uri clasice, dar și un DSP, un GPU, transco H265/AV1/VP9/…, un cip pentru a face AES etc. și conectați -l pe toate prin fabricarea IOD/Infinity. Prin urmare, fiecare producător de mașini/servere și-ar putea compune unitatea finală gata de utilizare prin a se compune și fără costuri de industrializare faramineuroasă în cercetare și dezvoltare.

Îmi amintește de conceptul de APU, dar nu știu dacă există un raport.

Acest răspuns a fost util

Mă întrebam cât de mult a reușit să ia în considerare o anumită evoluție în hardware (de asemenea Consumator-grad acea server-grade) în viitor, sau chiar o schimbare de paradigmă pe modul în care proiectăm mașini extrem de optime în general.

Anumite sisteme bine integrate (în special la Apple) nu se bazează exclusiv pe un procesor „clasic” foarte eficient, ci și pe mai multe jetoane auxiliare specializate care descarcă procesoare generaliste. Într -un sistem limitat ca smartphone, putem găsi cipuri de transcodare H265, unități de calcul pentru AI (Motor neural Apple) și, desigur, unitatea grafică clasică.

Prin urmare, preiau diagrama AMD EPYC de a 2 -a generație și mă întreb dacă Chiplets ar fi o modalitate simplă de a produce viabil din punct de vedere comercial și industrial din unitățile complete care îmbarcă mai multe cipuri specializate pentru a obține performanțe optime în anumite sarcini. De exemplu, o unitate ar putea asigura CCD -uri clasice, dar și un DSP, un GPU, transco H265/AV1/VP9/…, un cip pentru a face AES etc. și conectați -l pe toate prin fabricarea IOD/Infinity. Prin urmare, fiecare producător de mașini/servere și-ar putea compune unitatea finală gata de utilizare prin a se compune și fără costuri de industrializare faramineuroasă în cercetare și dezvoltare.

Îmi amintește de conceptul de APU, dar nu știu dacă există un raport.

Așadar, ar trebui să știți că un cip se face adesea cu IP (proprietate intelectuală): o funcție vândută destul de gata la nivelul „tranzistoarelor”, dar care trebuie să fie integrată în designul său.

Un exemplu clasic este un controler DDR3 pe microcontroller. Producătorul microcontrolerului nu stăpânește neapărat DDR3 și nu are abilități, timpul (nici dorința) de a crea un controler DDR3. Prin urmare, cumpără un IP de la un controlor și îl integrează în designul său.

Trebuie să reușești să vezi diferența dintre posibilitatea unui IP și un cip. Pentru mine, cipul este acolo pentru a aduce una sau mai multe funcții avansate și care au trecut deja testele gravurii, de aceea un pas suplimentar în proiectare. Dar rămâne problema testării solului complet cu toate cipurile. Deci nu putem crea sute de variații ca un Lego. Este nevoie de un minim de realitate economică.

Dar da, pentru un anumit volum putem crea prize la carte.

Marele avantaj este pe partea de producție a cipului: dacă un IP poate fi refuzat pentru diferite finețe de gravură, un cip în avantajul de a putea fi întotdeauna gravat în finețea sa inițială (dacă este suficient) atunci când alte părți pot cip să fie îmbunătățit cu gravură mai mică.

Acest răspuns a fost util

În afară de asta, am crezut că chipletele pot fi folosite într -un design modular. Faceți un design cu 4 jetoane, puricii cu defecțiuni sunt distribuite pe parcursul producției, iar cele cu 3 jetoane care funcționează pe 4 vor fi o gamă mai jos și puțin mai ieftină decât cele cu cei 4 care lucrează.

Care simplifică proiectarea și industrializarea în raport cu funcționarea convențională.

Iubitor de software gratuit și distribuție GNU/Linux Fedora. #Jesuisarius

Acest răspuns a fost util

Vă mulțumesc pentru acest mega articol interesant. Te -aș iubi prea mult timp pentru a detalia fiecare punct pe care nu -l explici în tutorial pentru a înțelege cu adevărat lucrurile, dar oricum interesant .

Utilizarea kiturilor de design de cipuri pentru a ajuta la deschiderea drumului pentru integrarea eterogenă 3D IC

Un chiplet este o matriță ASIC, proiectată și optimizată pentru funcționare în cadrul unui pachet în combinație cu alte cipuri. Integrat eterogen (HI) implică o matriță multiplă integrată sau chiplets în Chipplets în sistem în pachet (SIP). Aceste dispozitive oferite pentru a considera beneficii, a inclus performanță, putere, zonă, costuri și TTM.

Chiplet Design Exchange (CDX) este format din vânzători EDA, Chiplet

Furnizori/asamblatori și integratori SIP și este un grup de lucru deschis pentru a recomanda modele de cipuri standardizate și fluxuri de lucru pentru a facilita un ecosistem de cipuri. Acest webinar rezumă ofertele de kituri de design de cipuri (CDK) pentru a ajuta la standardizarea 2.5d și 3.D IC Designs pentru a crea un ecosistem deschis.

Construirea unui ecosistem pentru succes 2.Integrarea modelului 5D și 3D de cipuri

Similar cu un proces SOC, aveți nevoie de un ecosistem pentru Chipplets. Cheia permite adoptarea generală a pieței și implementarea proiectelor bazate pe chiplele incluzând:

- Tehnologie: 2.Procesele de fabricație și asamblare a matriței de 5 D

- IP: Modele de cipuri standardizate

- Fluxuri de lucru: fluxuri de design EDA și PDK, CDK, DRM și Reguli de asamblare

- Modele de afaceri: Marketplace Chiplet

Focusul inițial al CDX este 2.Modele de cipuri bazate pe interpunere 5D cu 3D de urmat. Aflați mai multe despre aceste eforturi în webinar.

Chiplet Design Exchange (CDX) este format din furnizori EDA, furnizori de cipuri/asamblatori și integratori SIP și este un grup de lucru deschis pentru a recomanda modele de cipuri standardizate și fluxuri de lucru pentru a facilita un ecosistem de cipuri. Acest webinar rezumă ofertele de kituri de design de cipuri (CDK) pentru a ajuta la standardizarea 2.5d și 3.D IC Designs pentru a crea un ecosistem deschis.

Construirea unui ecosistem pentru succes 2.Integrarea modelului 5D și 3D de cipuri

Similar cu un proces SOC, aveți nevoie de un ecosistem pentru Chipplets. Cheia permite adoptarea generală a pieței și implementarea proiectelor bazate pe chiplele incluzând:

- Tehnologie: 2.Procesele de fabricație și asamblare a matriței de 5 D

- IP: Modele de cipuri standardizate

- Fluxuri de lucru: fluxuri de design EDA și PDK, CDK, DRM și Reguli de asamblare

- Modele de afaceri: Marketplace Chiplet

Focusul inițial al CDX este 2.Modele de cipuri bazate pe interpunere 5D cu 3D de urmat. Aflați mai multe despre aceste eforturi în webinar.

Imaginea scursă dezvăluie un design ambițios de chiplet pentru GPU AMD Radeon

Imaginea scursă dezvăluie un design ambițios de chiplet pentru GPU AMD Radeon

- de

- În știri

- pe 16 august 2023

A apărut o imagine scursă, dezvăluind un design GPU cu Chiplets Radeon, presupus dintr -un proiect anulat al Navi 4C Chip 4C. Proiectarea prezentă între 13 și 20 de cipuri diferite pe un singur GPU, mărturisind abordarea ambițioasă AMD. Acest design mai complex de cipuri diferă de siliciul Navi 31 utilizat în prezent în Radeon RX 7900 XTX. În timp ce iterația anterioară a GPU a fost considerată o primă generație, nu a folosit un design real de cipuri precum recentele procesoare Ryzen ale AMD. Cu toate acestea, concepția despre Navi 4C dezvăluită reprezintă un avans semnificativ, deoarece încorporează mai multe cipuri de calcul, precum și chipuri de I/O distincte, pe un singur substrat. Imaginea scursă prezintă 13 cipuri, cu posibilitatea ca cipurile de control de memorie suplimentare să nu fie afișate pe imagine.

Pentru a confirma autenticitatea imaginii, este evidențiat un brevet relevant din 2021 care discută conceptul de modularitate în procesoare paralele. Modelele de brevet seamănă îndeaproape cu designul prezentat în imaginea scursă, ceea ce sugerează chiar posibilitatea mai multor cipuri din cealaltă parte a cupei transversale.

Din păcate, designul GPU prezentat în imaginea scursă a fost anulat. Acest lucru este de acord cu relațiile recente care sugerează că accentul AMD pentru următoarea generație de GPU va fi pe cipurile monolitice Navi 43 și Navi 44 destinate publicului larg, mai degrabă decât pe componente înalte. Cu toate acestea, se speculează că AMD își redirecționează eforturile către dezvoltarea unui GPU compus din mai multe cipuri de calcul pentru segmentul ridicat al gamei sale viitoare de cărți grafice, potențial cu ADNA 5.

Deși realizarea mai multor cipuri de calcul pentru graficele de joc este mai complexă decât pentru calculele tradiționale ale CPU, decizia AMD de a depăși obstacolele de proiectare acum și de a lucra la o soluție mai bună pentru ADNA 5 este percepută ca un pas pozitiv. Ar fi fost avantajos ca AMD să aibă un plan de salvare, cum ar fi un nou nod pentru o versiune îmbunătățită a Navi 31.